Communication série au sein d'un système : Bus I2C⚓

Bus série / parallèle⚓

Dans un système les composants ont très souvent besoin d'être reliés entre eux pour communiquer (transfert de donnée, envoie d'instruction, ...). Lorsque ces composants sont nombreux, plutôt que d'ajouter pour chaque composant des liens directs, chaque composant est relié à un bus.

Un Bus est caractérisé par

Une Fréquence

Un nombre de bit qu'il peut transmettre simultanément

Lorsqu'un bus peut transmettre plus d'un bit d'information simultanément, on parle de bus parallèle, sinon d'un bus série.

Pour connecter un disque dur à une carte mère on utilise soit de l'IDE (bus parallèle) soit du SATA (bus série)

Bus parallèle⚓

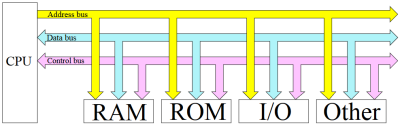

La figure ci-contrre représente une vue schématique du flux d'information circulant dans un système à microprocesseur (CPU). Dans ce système le CPU sélectionne, via le bus d'adresse, le périphérique avec lequel il souhaite échanger des données par le bus de donnée (Data Bus). Le bus de contrôle lui peut indiquer le sens de cette communication (lecture ou écriture). Cet aiguillage, très employé dans les systèmes à base de processeur, permet d'alléger les connections directes au CPU.

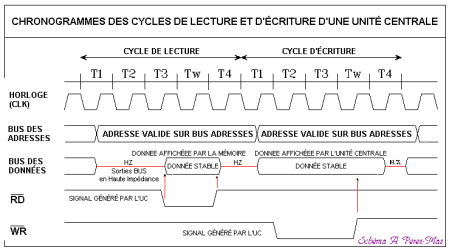

Le chronogramme suivant représente les différents signaux numériques circulant lors d'un cycle de lecture puis d'écriture d'une unité centrale. Tous ces composants sont cadencés par une Horloge (CLK) la lecture est commandée par un front descendant de RD\ et l'écriture par un front descendant de WR\.

Bus série⚓

Un bus série permet de transmettre les informations bit par bit. Il comporte cependant plus d'une ligne permettant de transmettre des informations par l'addition d'éventuels signaux de contrôle et généralement par l'utilisation de deux lignes distinctes permettant ainsi à ces bus d'être bidirectionnels afin de permettre la transmission d'information dans les deux directions simultanément.

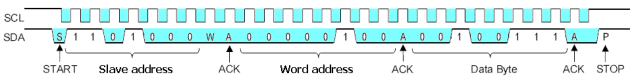

Le chronogramme ci-dessus est un exemple de « trame » I2C (voir plus loin). Le bus série transmettant les données bit par bit, il est nécessaire lorsque l'on veut par exemple transmettre un mot de 32 bits de sérialiser l'information pour sa transmission. Ceci nécessite des composants additionnels.

L'intérêt principal de ce type de bus (outre un câblage simplifié par rapport à un bus parallèle) est que pour un coût moindre (grâce au faible nombre de conducteurs de données) il permet - en faisant appel à des composants électroniques de haute qualité - de dépasser les débits atteints par des bus parallèles.

Utilisation : Disque durs récents (FC, SAS, ou SATA), une liaison USB peut être apparentée à un Bus série, communication dans les systèmes embarqués (Bus I2C), automobile (Bus CAN), ...

BUS I2C⚓

Le bus I2C (Inter Integrated Circuit Bus) est le bus historique, devenu standard, développé par Philips dans les années 80, pour permettre de relier facilement à un microprocesseur divers circuits intégrés (spécialisés dans le stockage et l'affichage de données, dans l'exécution de fonction numériques ou analogiques diverses). Aujourd'hui d'innombrables périphériques utilisent ce bus, (appareils TV et vidéo, dans les systèmes audio et radio, postes téléphoniques, systèmes électroniques automobiles, PC, appareils électroménagers, etc.).

Description du bus

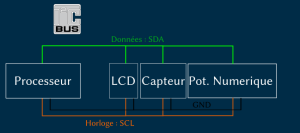

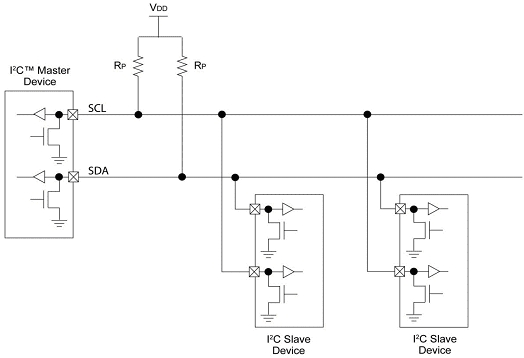

Le bus I2C permet de faire communiquer, des composants électroniques très divers grâce à seulement trois fils :

un signal de donnée ( SDA )

un signal d'horloge ( SCL )

un signal de référence électrique ( Masse )

Dans sa version de base, les données sont transmises en série à 100 kbits/s en mode standard. Ce qui ouvre la porte de cette technologie à toutes les applications où la vitesse n'est pas primordiale.

La révision de la norme en 1992 autorise de nouveaux modes de fonctionnement :

vitesse de transfert portée de 100 à 400 kbits/s, voire 3,4Mbits/s en mode HV

adressage des circuits étendu de 7 à 10 bits.

De nombreux fabricants ayant adopté le système, la variété des circuits disponibles disposant d'un port I2C est énorme : Ports d'E/S bidirectionnels, Convertisseurs A/N et N/A, mémoires (RAM, EPROM, EEPROM, etc...), Circuits Audio (Egaliseur, Contrôle de volume, ...) et autre drivers (LED , LCD , ...).

Conseil : Précautions : Résistance de tirage

Afin de d'éviter les conflits électriques les Entrées/Sorties, SDA et SCL sont de type "Collecteur Ouvert" (ou "Drain Ouvert"). Les sorties étant à collecteur (ou drain) ouvert la tension de sortie à l'état haut est la tension « ramenée » par les résistances de rappel (qui sont connectées à la ligne d'alimentation des circuits « VDD »).

Cette technique permet entre autre la communication entre dispositifs réalisés dans des technologies différentes et utilisant éventuellement des tensions d'alimentation différentes.

Exemple :

Pour les dispositifs fonctionnant sous une tension de 5V ± 10%, les niveaux d'entrée sont :

Niveau bas : VILmax = 1,5V

Niveau haut : VIHmin = 3V

Dans tous les cas la tension de sortie à l'état bas est VOLmax = 0,4V

Protocole du bus I2C⚓

Définition :

Émetteur : Unité qui envoie les données sur le bus.

Récepteur : Unité qui reçoit les données du bus.

Maître : Unité qui démarre un transfert, génère des signaux d'horloge et met fin au transfert.

Esclave : Unité adressée par le maître.

Multi-maître : Possibilité pour plusieurs maîtres de tenter de prendre le contrôle du bus en même temps, sans altérer le message.

Arbitrage : Procédure permettant de résoudre les conflits d'accès des maîtres au bus et d'éviter l'altération du message. Le contrôle du bus n'est accordé qu'à un maître à la fois.

SDA : Ligne des signaux de données.

SCL : Ligne des signaux d'horloge.

Le protocole de communication doit prendre en compte les règles suivantes :

une distinction entre les circuits maîtres (ceux qui décident du dialogue) et les circuits esclaves,

une identification des circuits,

un acquittement des transferts (confirmation par les circuits de la bonne réception des informations qui leur ont été transmises),

un système de priorité en cas de conflit.

Les modes les plus utilisés sont les suivants :

Au repos (en l'absence de transmission).

Le maître veut lire une information contenue dans un circuit esclave.

Le maître veut écrire une information dans un circuit esclave.

Le maître veut lire une information contenue dans un circuit esclave.

Dans le second cas le déroulement de la séquence sera :

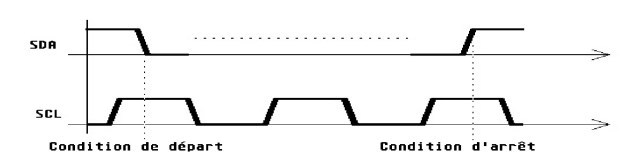

étape 1 : Condition de départ

Un front descendant est appliqué sur la ligne SDA quand SCL est encore au niveau haut

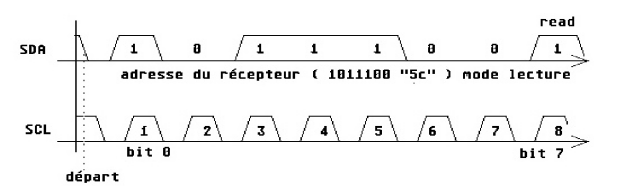

étape 2 : Transmission de l'adresse ( premier octet )

A chaque niveau haut de SCL, un bit de donnée sur SDA (en commençant par les bits de poids fort) est transmis par le maître. Ce premier octet contient :

7 premiers bits correspondants à l'adresse du circuit désiré

le dernier bit B0 correspondant au mode transfert : B0=1 pour une lecture/B0=0 pour une écriture

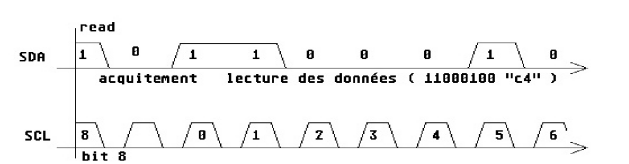

étape 3 : Acquittement

Après chaque octet reçu, le récepteur doit générer un signal d'acquittement. Pour cela, durant le niveau haut de SCL qui suit la transmission de l'octet, le récepteur (l'esclave dans ce cas ) met la ligne SDA au niveau bas.

étape 4 : Transmission du deuxième octet ( lecture)

Durant chaque niveau haut sur SCL, l'esclave (ici émetteur) envoie 8 bits de donnée (en commençant toujours par le bit de poids fort).

Après une bonne réception, c'est le circuit maître qui doit générer le signal d'acquittement en maintenant la ligne SDA au niveau bas durant le niveau haut de SCL. Dans le cas où le récepteur n'est pas en mesure de recevoir les données, il doit mettre la ligne SCL au niveau bas pour mettre l'émetteur en attente.

étape 5 : Condition d'arrêt

Un front montant est appliqué sur la ligne SDA quand SCL est au niveau haut.

Le maître veut écrire une information dans un circuit esclave.

Les étapes 1, 2, 3 et 5 sont identiques au cas précédent. Au niveau de l'étape 4 c'est le maître qui va émettre de la même façon qu'il transmet les adresses.

Exemple :

Conclusion⚓

De part sa conception, ce système permet donc un dialogue souple et des réalisations très modulaires (seulement deux fils à connecter). Ce type de connexion présente aussi un avantage économique (réduction du prix des boîtiers et de la connectique associée). De plus, au niveau des études, il est facile de réutiliser des modules ou des sous-programmes déjà fabriqués.